-

Dubhe-90

High Performance 64-bit RISC-V Processor

data centers, PC, mobile devices, high-performance network communications, and machine learning

-

Dubhe-80

64-bit application processor for energy-efficient computation

mobile, desktop, AI, and automotive

-

StarNoC-500

StarFive's first self-developed interconnect fabric IP with cache coherence support

supporting the construction of multi-cores and SoC to provide cache coherence NoC

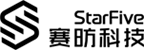

E2 Series

The E2 Series is highly optimized for area and power while still offering class-leading performance. Targeted for microcontrollers and embedded devices, the E2 Core can be configured to be as small as 13.5k gates with an efficient 2‑stage pipeline or configured for higher performance with a 3‑stage pipeline, hardware floating-point, instruction cache, and more.

Feature

Configurable core performance

Floating Point Unit, supporting Double, Single, and Half precision

Custom memory map and ports

Optional Tightly Integrated Memory (TIM)

RV32E support with the smallest core configuration as small as 13.5k gates and is .005mm2 in 28nm

Bit manipulation extension

Application

MEMS Sensors

Power management

Digital motor control

Low-power MCUs

Health wearable monitors

Environmental monitors

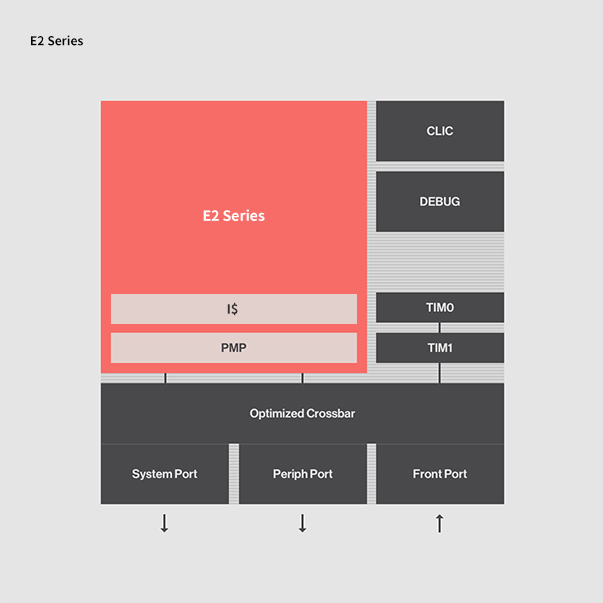

E3 Series

The E3 Series is highly-integrated and feature-rich. It includes the E31 Core, which is the most widely deployed RISC‑V core in the world. E3 embedded cores have a 5-6 stage pipeline, offering a great balance between performance and efficiency.

Feature

Up to 8 coherent E3 Cores and optional L2 Cache Controller

Optional Single or Double precision Floating Point Unit

Level 1 Memory System and ECC

Number, type, and width of bus interfaces

Support for SiFive Insight Advanced Trace and Debug

Application

Consumer Electronics

Motor Control

Industrial Automation

Storage

High-performance embedded

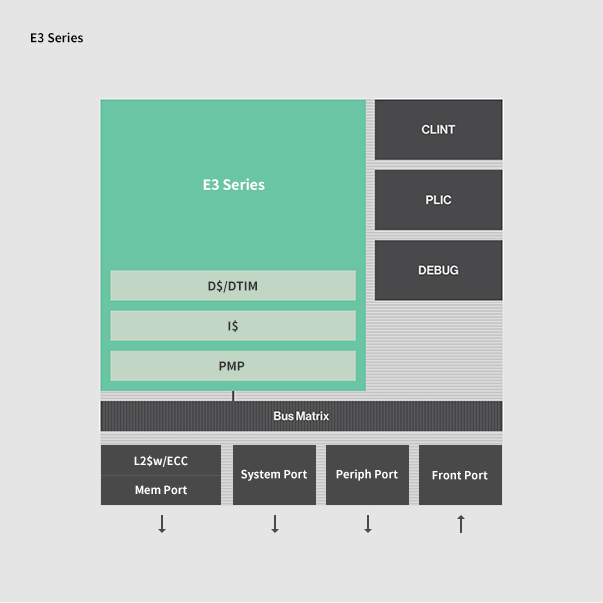

E7 Series

The E7 Series offers a 32-bit embedded processor targeting applications that require high performance while maintaining energy efficiency. The E7 core has a superscalar 8-stage in-order pipeline.

Feature

E7 core architectural features

- RV32GCV capable core

- Dual Issue, in-order 8-stage Harvard Pipeline

PPA

- DMIPS – 2.5 DMIPS / MHz

- Coremark – 5.1 CoreMarks / MHz

- The core area is only 30% larger than that of the 3 series of cores with the same configuration

Very flexible memory system

- Optional I$ and D$

- Optional I and D TIM interfaces

- Optional Fast IO Port (FIO) per core

Functional Safety and Security and Real Time

- In level 1 and level 2 caches, single error correction and double error detection code ECC function are optional.

- Programmatically clear and/or disable dynamic branch prediction for deterministic execution and enhanced security

Multi-core capable with coherency and optional L2

Application

SSD controller

IoT edge computing

Wireless broadcast

Automobile/Industry